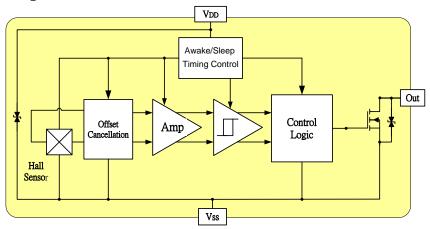

MH179 Hall-effect latch is a temperature stable, stress-resistant, mini-power IC. Superior high-temperature performance is made possible through a dynamic offset cancellation that utilizes chopper-stabilization. This method reduces the offset voltage normally caused by device over molding, temperature dependencies, and thermal stress.

MH179 includes the following on a single silicon chip: voltage regulator, Hall voltage generator, small-signal amplifier, chopper stabilization, Schmitt trigger, open-drain output. Advanced CMOS wafer fabrication processing is used to take advantage of low-voltage requirements, component matching, very low input-offset errors, and small component geometries.

This device requires the presence of both south and north polarity magnetic fields for operation. In the presence of a south polarity field of sufficient strength, the device output sensor on, and only switches off when a north polarity field of sufficient strength is present.

MH179 is rated for operation between the ambient temperatures  $-40^{\circ}$ C and  $+85^{\circ}$ C, and  $-40^{\circ}$ C to  $125^{\circ}$ C for the K temperature range. for the E temperature range. The two package styles available provide magnetically optimized solutions for most applications. Package SO is an SOT-23, a miniature low-profile surface-mount package, while package UA is a three-lead ultra mini SIP-3 for through-hole mounting.

The package type is in a lead Halogen Free version was verified by third party Lab.

### Features and Benefits

- CMOS Hall IC Technology

- Strong RF noise protection

- 2.0 to 5.5V for battery-powered applications

- Operation down to 2.0V, Micro power consumption

- 100% tested at 125°C for K

- Low sensitivity drift in crossing of Temp range

- Ultra Low power consumption at 600uA (Avg)

- High ESD Protection, HBM  $> \pm 4$ KV( min )

- Open Drain output

- RoHS compliant 2011/65/EU and Halogen Free

#### **Applications**

- Speed sensing

- Position sensing

- Revolution counting

- Solid-State Switch

- Current sensing

- Revolution counting

- Solid-State Switch

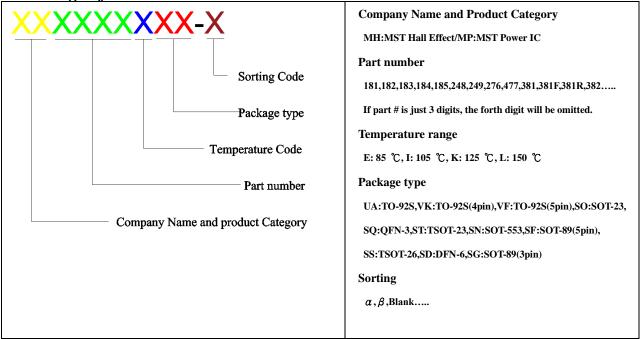

**Ordering Information**

| Part No. | Temperature Suffix                                      | Package Type |  |

|----------|---------------------------------------------------------|--------------|--|

| MH179KUA | $K (-40^{\circ}C \text{ to} + 125^{\circ}C)$            | UA (TO-92S)  |  |

| MH179EUA | $E (-40^{\circ}C \text{ to } + 85^{\circ}C)$            | UA (TO-92S)  |  |

| MH179ESO | $E \left(-40^{\circ}C \text{ to } + 85^{\circ}C\right)$ | SO (SOT-23)  |  |

Custom sensitivity selection is available by MST sorting technology

### Functional Diagram

Note: Static sensitive device; please observe ESD precautions. Reverse  $V_{DD}$  protection is not included. For reverse voltage protection, a  $100\Omega$  resistor in series with  $V_{DD}$  is recommended.

Absolute Maximum Ratings At (Ta=25°C)

| Characteristics                            |                         |             | Values      | Unit  |

|--------------------------------------------|-------------------------|-------------|-------------|-------|

| Supply voltage,(VDD)                       |                         |             | 6           | V     |

| Output Voltage,(Vout)                      |                         |             | 6           | V     |

| Reverse voltage, (VDD) (VOUT)              |                         |             | -0.3        | V     |

| Magnetic flux density                      |                         |             | Unlimited   | Gauss |

| Output current,( <i>Iovr</i> )             |                         |             | 10          | mA    |

| On anoting Towns and true Pane             | "E" version             |             | -40 to +85  | °C    |

| Operating Temperature Range                | e, ( <i>1a</i> )        | "K" version | -40 to +125 | °C    |

| Storage temperature range, ( <i>Ts</i> )   |                         |             | -65 to +150 | °C    |

| Maximum Junction Temp, $(Tj)$              |                         |             | 150         | °C    |

| Thermal Resistance                         | $(\theta_{JA})$ UA / SO |             | 206 / 543   | °C/W  |

|                                            | $(\theta_{JC})$ UA / SO |             | 148 / 410   | °C/W  |

| Package Power Dissipation, $(P_D)$ UA / SO |                         |             | 606 / 230   | mW    |

**Note:** Exceeding the absolute maximum ratings may cause permanent damage. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability.

### **Electrical Specifications**

DC Operating Parameters  $T_A=+25$  °C,  $V_{DD}=3.0V$

| Parameters                      | <b>Test Conditions</b>                                                           |     | Тур  | Max  | Units |

|---------------------------------|----------------------------------------------------------------------------------|-----|------|------|-------|

| Supply Voltage, $(V_{DD})$      | Operating                                                                        |     |      | 5.5  | V     |

|                                 | Awake State                                                                      |     | 2.0  | 5.0  | mA    |

| Supply Current,( $I_{DD}$ )     | Sleep State                                                                      |     | 7.0  | 10.0 | uA    |

|                                 | Average                                                                          |     | 600  | 1000 | uA    |

| Output Saturation Voltage,      | Iout=5mA,B>BOP                                                                   |     |      | 200  | mV    |

| Output Leakage Current,(Ioff)   | IOFF B <brp, vout="5.5V&lt;/td"><td></td><td></td><td>1.0</td><td>uA</td></brp,> |     |      | 1.0  | uA    |

| Awake mode time,( <i>Taw</i> )  | Operating                                                                        |     | 40   | 80   | uS    |

| Sleep mode time,( <i>TSL</i> )  | Operating                                                                        |     | 160  | 320  | uS    |

| Duty Cycle, $(D,C)$             |                                                                                  |     | 20   |      | %     |

| Response Time, $(T_{RES})$      |                                                                                  |     |      | 2000 | Hz    |

| Output Rise Time, $(T_R)$       | $RL=1K\Omega$ , $CL=20pF$                                                        |     | 0.18 | 0.45 | uS    |

| Output Fall Time, ( <i>TF</i> ) | RL=1KΩ; CL =20pF                                                                 |     | 0.18 | 0.45 | uS    |

| Electro-Static Discharge        | НВМ                                                                              | 4   |      |      | KV    |

| Operating Point (BOP)           | S pole to branded side, B > BOP, Vout On                                         | 5   |      | 40   | Gauss |

| Release Point (BRP)             | N pole to branded side, B < BRP, Vout                                            | -40 |      | -5   | Gauss |

| Hysteresis (BHYS)               | BOP - BRP                                                                        |     | 40   |      | Gauss |

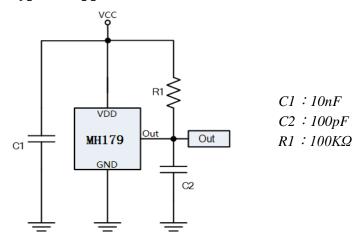

### Typical Application circuit

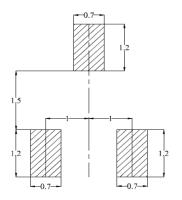

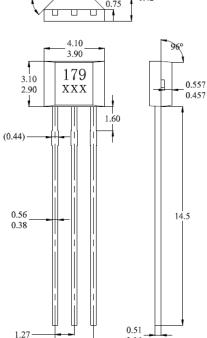

### Sensor Location, Package Dimension and Marking **UA Package**

# 4.10 3.90

#### **NOTES:**

- 1. Controlling dimension: mm

- 2. Leads must be free of flash and plating voids

- 3. Do not bend leads within 1 mm of lead to package interface.

- 4. PINOUT:

Pin 1 VDD Pin 2 **GND** Pin 3 Output

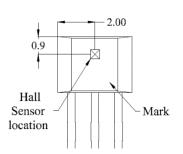

#### **Hall Chip location**

### **Output Pin Assignment** (Top view)

179 XXX

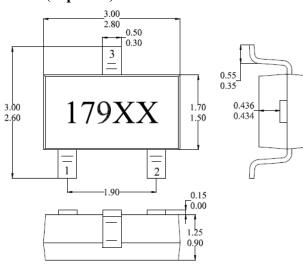

# SO Package (Top View)

#### **NOTES:**

- 1. PINOUT (See Top View at left :)

- $Pin \ 1 \qquad V_{DD}$

- Pin 2 Output

- Pin 3 GND

- 2. Controlling dimension: mm

- 3. Lead thickness after solder plating will be 0.254mm maximum

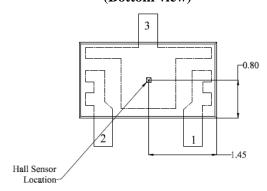

## Hall Plate Chip Location (Bottom view)

#### (For reference only)Land Pattern