### **Ultra-Low power CMOS Output Hall Switch**

MH235 Hall-effect sensor is a temperature stable, stress-resistant, Low Tolerance of Sensitivity Ultra-power switch. Superior high-temperature performance is made possible through a dynamic offset cancellation that utilizes chopper-stabilization. This method reduces the offset voltage normally caused by device over molding, temperature dependencies, and thermal stress.

MH235 is special made for low operation voltage, 2.7V, to active the chip which is includes the following on a single silicon chip: voltage regulator, Hall voltage generator, small-signal amplifier, chopper stabilization, Schmitt trigger, CMOS output driver. Advanced CMOS wafer fabrication processing is used to take advantage of low-voltage requirements, component matching, very low input-offset errors, and small component geometries. This device requires the presence of omni-polar magnetic fields for operation.

The package type is in a Halogen Free version has been verified by third party Lab.

### Features and Benefits

- Output-on & Inverted Output-on without Magnet present in one chip

- Low and high Hz presented in one chip

- Strong RF noise protection

- 2.7 to 5.5V for battery-powered applications

- Omni polar, output switches with absolute value of North or South pole from magnet

- Operation down to 2.7V

- High Sensitivity for reed switch replacement applications

- Multi Small Size option

- Low sensitivity drift in crossing of Temp. range

- Ultra-Low power consumption at 1.6uA (Avg)

- High ESD Protection, HBM>±4KV( min )

- Totem-pole output

- RoHS compliant 2011/65/EU and Halogen Free.

### **Applications**

- Solid state switch

- Handheld Wireless Handset Awake Switch

- Lid close sensor for battery powered devices

- Magnet proximity sensor for reed switch replacement in low duty cycle applications

- Floating Meter

- Security

- 3C

- Smart Meter

- TWS

### **Ultra-Low power CMOS Output Hall Switch**

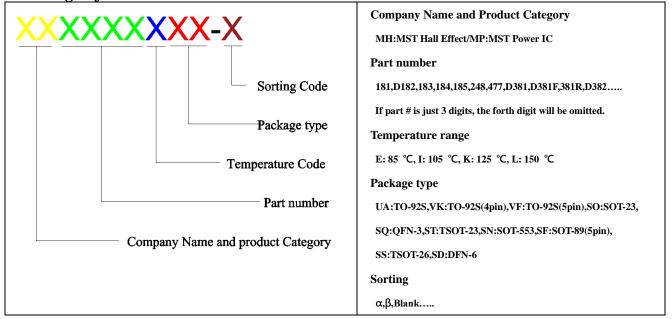

### **Ordering Information**

| Part No. | Temperature Suffix                                      | Package Type   |

|----------|---------------------------------------------------------|----------------|

| MH235EST | $E \left(-40^{\circ}C \text{ to } + 85^{\circ}C\right)$ | ST(TSOT-23)    |

| MH235EUA | $E \left(-40^{\circ}C \text{ to } + 85^{\circ}C\right)$ | UA(TO-92S)     |

| MH235ESD | E $(-40^{\circ}\text{C to } +85^{\circ}\text{C})$       | SD (DFN2X2-6L) |

| MH235ESS | E $(-40^{\circ}\text{C to} + 85^{\circ}\text{C})$       | SS (QFN1x1-4L) |

Custom sensitivity selection is available by MST sorting technology

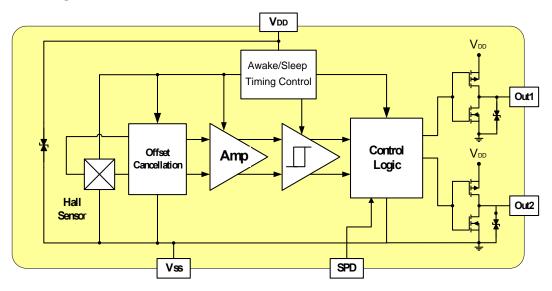

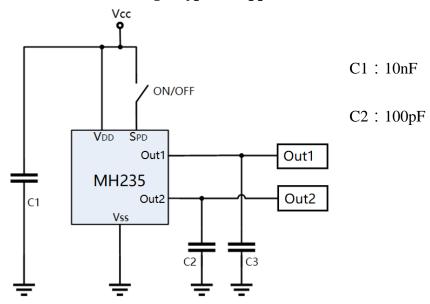

## Functional Diagram

Note: Static sensitive device; please observe ESD precautions. Reverse  $V_{DD}$  protection is not included. For reverse voltage protection, a  $100\Omega$  resistor in series with  $V_{DD}$  is recommended.

MH 235, HBM>±4KV which is verified by third party lab.

## **Ultra-Low power CMOS Output Hall Switch**

Absolute Maximum Ratings At(Ta=25°C)

| Characteristics                                          |                                | Values          | Unit  |

|----------------------------------------------------------|--------------------------------|-----------------|-------|

| Supply voltage,(VDD)                                     |                                | 6               | V     |

| Output Voltage,(Vout)                                    |                                | 6               | V     |

| Magnetic flux density                                    |                                | Unlimited       | Gauss |

| Output current,(Iovr)                                    |                                | 5               | mA    |

| Operating temperature range, (Ta)                        |                                | -40 to +85      | °C    |

| Storage temperature range, (Ts)                          |                                | -65 to +150     | °C    |

| Maximum Junction Temp,(Tj)                               |                                | 150             | °C    |

| Thermal Resistance                                       | (θ <sub>JA</sub> ) UA/ST/SS/SD | 206/543/300/160 | °C/A  |

|                                                          | (θ <sub>JC</sub> ) UA/ST/SS/SD | 148/410/52/35   | °C/A  |

| Package Power Dissipation, (P <sub>D</sub> ) UA/ST/SS/SD |                                | 606/400/416/780 | mW    |

**Note:** Exceeding the absolute maximum ratings may cause permanent damage. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability.

## **Electrical Specifications**

DC Operating Parameters: Ta=25°C, VDD=3.0V

| Parameters                                 | <b>Test Conditions</b> | Min                  | Тур         | Max       | Units |

|--------------------------------------------|------------------------|----------------------|-------------|-----------|-------|

| Supply Voltage, $(V_{DD})$                 | Operating              | 2.7                  |             | 5.5       | Volts |

|                                            | Awake State            |                      | 2.0         |           | mA    |

| Supply Current, ( <i>I</i> <sub>DD</sub> ) | Sleep State            |                      | 1.0         |           | μΑ    |

|                                            | Average (SPD=Hi)       |                      | 1.6(135)    |           | μΑ    |

| Output High Voltage, (VoH)                 | IOUT=1.0mA (Source)    | V <sub>DD</sub> -0.2 |             |           | V     |

| Output Low Voltage, (Vol)                  | Iout=1.0mA (Sink)      |                      |             | 0.2       | V     |

| Awake mode time, ( <i>Taw</i> )            | Operating              |                      | 20          | 40        | uS    |

| Sleep mode time, ( <i>Tsl.</i> )           | Operating (SPD=Hi)     |                      | 80(0.16)    | 150(0.32) | mS    |

| Duty Cycle, ( <i>D</i> , <i>C</i> )        | (SPD=Hi)               |                      | 0.025(12.5) |           | %     |

| Power-On Time, $(T_{PO})$                  |                        |                      | 16          | 32        | nS    |

| Output Switch Time, $(T_{SW})$             | Operating (SPD=Hi)     |                      | 80(0.2)     | 160(0.4)  | mS    |

| Output Switch Frequency, $(F_{SW})$        | Operating (SPD=Hi)     | 15(6.5k)             |             |           | Hz    |

| Electro-Static Discharge                   | HBM                    | 4                    |             |           | KV    |

| Operate Point, BOPS(BOPN)                  | B>B <sub>OP</sub> X    | 20(-55)              |             | 55(-20)   | Gauss |

| Release Point, BRPS(BRPN)                  | B <b<sub>RPX</b<sub>   | 10(-45)              |             | 45(-10)   | Gauss |

| Hysteresis, (BHYS)                         | BOPX - BRPX            |                      | 10          |           | Gauss |

## **Ultra-Low power CMOS Output Hall Switch**

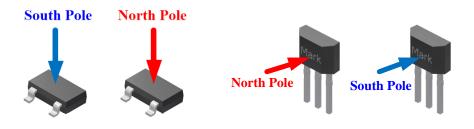

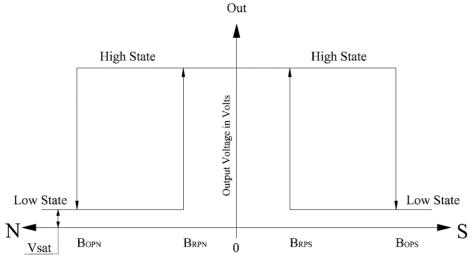

## MH235 ST/UA Output Behavior versus Magnetic Polar

DC Operating Parameters:  $Ta = -40 \text{ to } 85^{\circ}\text{C}$ , Vdd = 2.7V to 5.5V

| Parameter                   | Test condition                          | OUT  |

|-----------------------------|-----------------------------------------|------|

| South pole                  | B>Bop-S                                 | Low  |

| Null or weak magnetic field | $B=0 \text{ or } B < \mid B_{RP}X \mid$ | High |

| North pole                  | B> Bop-N                                | Low  |

ST Package

**UA Package**

## Output Behavior

Magnetic Flux Density in Gauss

## **Ultra-Low power CMOS Output Hall Switch**

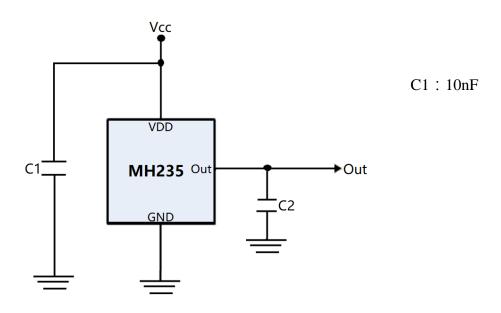

## ST and UA package Typical Application Circuit

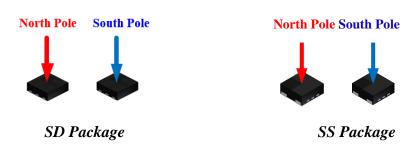

## MH235 SS/SD Output Behavior versus Magnetic Polar

DC Operating Parameters:  $Ta = -40 \text{ to } 85^{\circ}\text{C}$ , Vdd = 2.7V to 5.5V

| Parameter                   | Test condition                           | OUT1 | OUT2 |

|-----------------------------|------------------------------------------|------|------|

| South pole                  | B>Bop-S                                  | Low  | High |

| Null or weak magnetic field | $B=0 \text{ or } B < \mid B_{RP}-X \mid$ | High | Low  |

| North pole                  | B> Bop-N                                 | Low  | High |

## Output Behavior

## **Ultra-Low power CMOS Output Hall Switch**

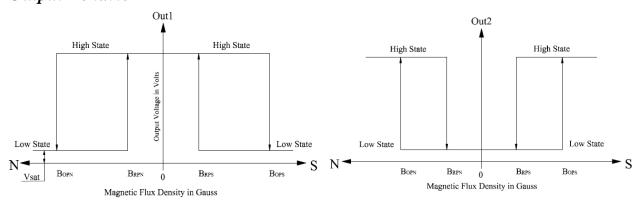

## SS and SD Package Typical Application circuit

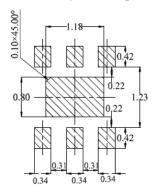

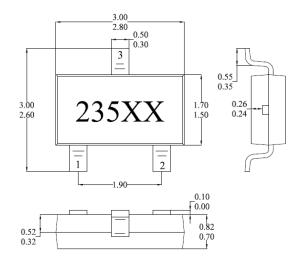

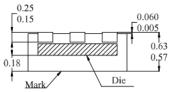

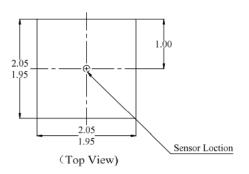

# Sensor Location, package dimension and marking ST Package (TSOT-23)

(Top View)

### **NOTES:**

- PINOUT (See Top View at left :)

Pin 1 V<sub>DD</sub>; Pin 2 Output; Pin 3 GND

- 2. Controlling dimension: mm

- 3. Lead thickness after solder plating will be 0.254mm maximum

- 4. XX: Date Code, Refer to DC table

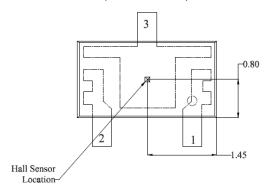

# Hall Plate Chip Location (Bottom view)

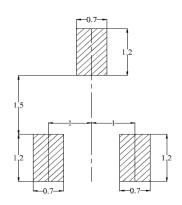

### (For reference only) Land Pattern

### **Ultra-Low power CMOS Output Hall Switch**

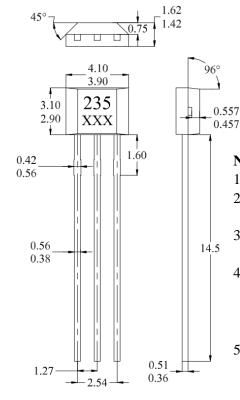

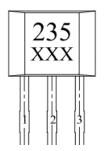

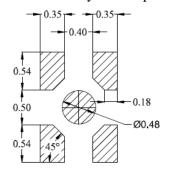

#### **UA Package (TO-92)**

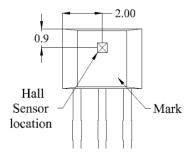

## **Hall Chip location**

### **Output Pin Assignment**

### (Top view)

### **NOTES:**

- 1. Controlling dimension: mm

- 2. Leads must be free of flash and plating voids

- 3. Do not bend leads within 1 mm of lead to package interface.

- 4. PINOUT:

Pin 1 VCC Pin 2 GND Pin 3 Output

5. XXX; 1<sup>st</sup> X=Year; 2<sup>nd</sup> and 3<sup>rd</sup> XX=Week

### **SS Package (DFN 1.0\*1.0-4L)**

#### **NOTES:**

- 1. Controlling dimension: mm

- 2. Leads must be free of flash and plating voids

- 3. Lead thickness after solder plating will be 0.254mm maximum

### 4. PINOUT:

| Pin No. | Pin Name    | Function     |

|---------|-------------|--------------|

| 1       | $V_{ m DD}$ | Power Supply |

| 2       | Vss         | Ground       |

| 3       | Vout        | Output1      |

| 4       | Vout        | Output2      |

| 5       | PAD         | Ground       |

4. (For reference only) Land pattern

## Ultra-power, Totem Pole Output Hall Effect Switch

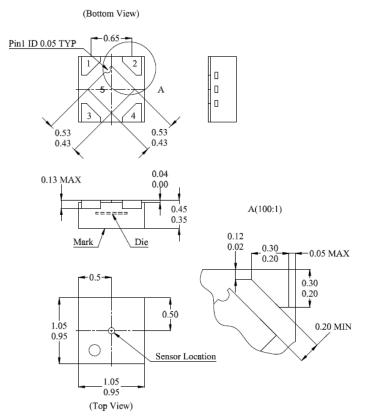

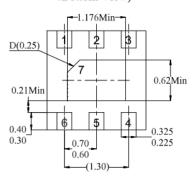

### SD package (DFN2\*2-6L)

(Bottom View)

### **NOTES:**

- 1. Controlling dimension: mm

- 2. Leads must be free of flash and plating voids

- 3. Lead thickness after solder plating will be 0.254mm maximum

### 4. PINOUT:

| Pin No. | Pin Name          | Function     |

|---------|-------------------|--------------|

| 1       | $V_{\mathrm{DD}}$ | Power Supply |

| 2       | Vout              | Output2      |

| 3       | Vout              | Output1      |

| 4       | N.C               | N.C          |

| 5       | Vss               | Ground       |

| 6       | SPD               | Set pin      |

| 7       | PAD               | Ground       |

5. (For reference only) Land pattern